Cамоучитель по Assembler

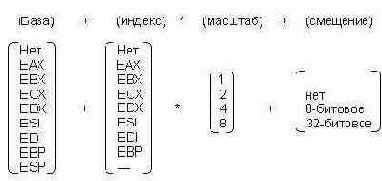

Режимы косвенной адресации с использованием 32-разрядных регистров.

Прочерк во второй колонке подчеркивает, что регистр ESP нельзя использовать в качестве индексного. Это не означает, что ESP нельзя указывать в качестве второго операнда:

mov ЕАХ,[ЕСХ][ESP]

Недопустима только конструкция, в которой содержимое ESP умножается на масштабирующий множитель:

mov ЕАХ,[ЕСХ][ESP*8]

Полезно также отметить, что смещение в команде вида

mov ЕАХ,[ЕВХ][ЕСХ]+20

может быть только или 8-битовым, или 32-битовым. 16-битовые смещения не образуются. Если указанная в команде величина смещения помещается в байт, как это имеет место в приведенном выше примере команды, то смещение в коде команды занимает 1 байт. Если же величина смещения больше 255, то под него в коде команды отводится сразу 32 бит.

Таким образом, понятия базовой и индексной адресации в 32-разрядных процессорах несколько размываются. Если регистр указывается с масштабирующим множителем, то это, конечно, индексная адресация. Если же множитель отсутствует, то адресацию и через ЕВХ, и через ESI с равным успехом можно отнести как к базовой, так и к индексной.

Использование для адресации памяти 16-разрядных регистров резко сужает возможности адресации 32-разрядных процессоров (Рисунок 4.3). В этом случае мы фактически имеем дело с МП 86.